- 실제로 워런 버핏이 코카콜라에 투자한 여러 가지 이유 중 하나는 음식료 산업의 특성상 매년 집 행해야 하는 설비 투자 규모가 여타 제조업에 비해 적은 편이고, 이로 인해 전사 매출액 대비 감가상각비 비중이 적다는 점이 투자 자 입장에서 매력적이기 때문이었다. 이에 반해 삼성전자는 매년 10조 원 이상 투자를 집행하고 있으며, 제품의 성능을 개선하고 경쟁 격차를 유지하기 위해 영업이익이 얼마든 상관없이 매년 일 정 규모 이상의 투자를 집행해야 한다. 이로 인해 삼성전자의 재 무제표에선 막대한 상각비가 매년 지속적으로 높은 비중을 차지 하고 있다. 이는 가치투자를 지향하는 투자자에게 성가신 변수가 될 수밖에 없다.

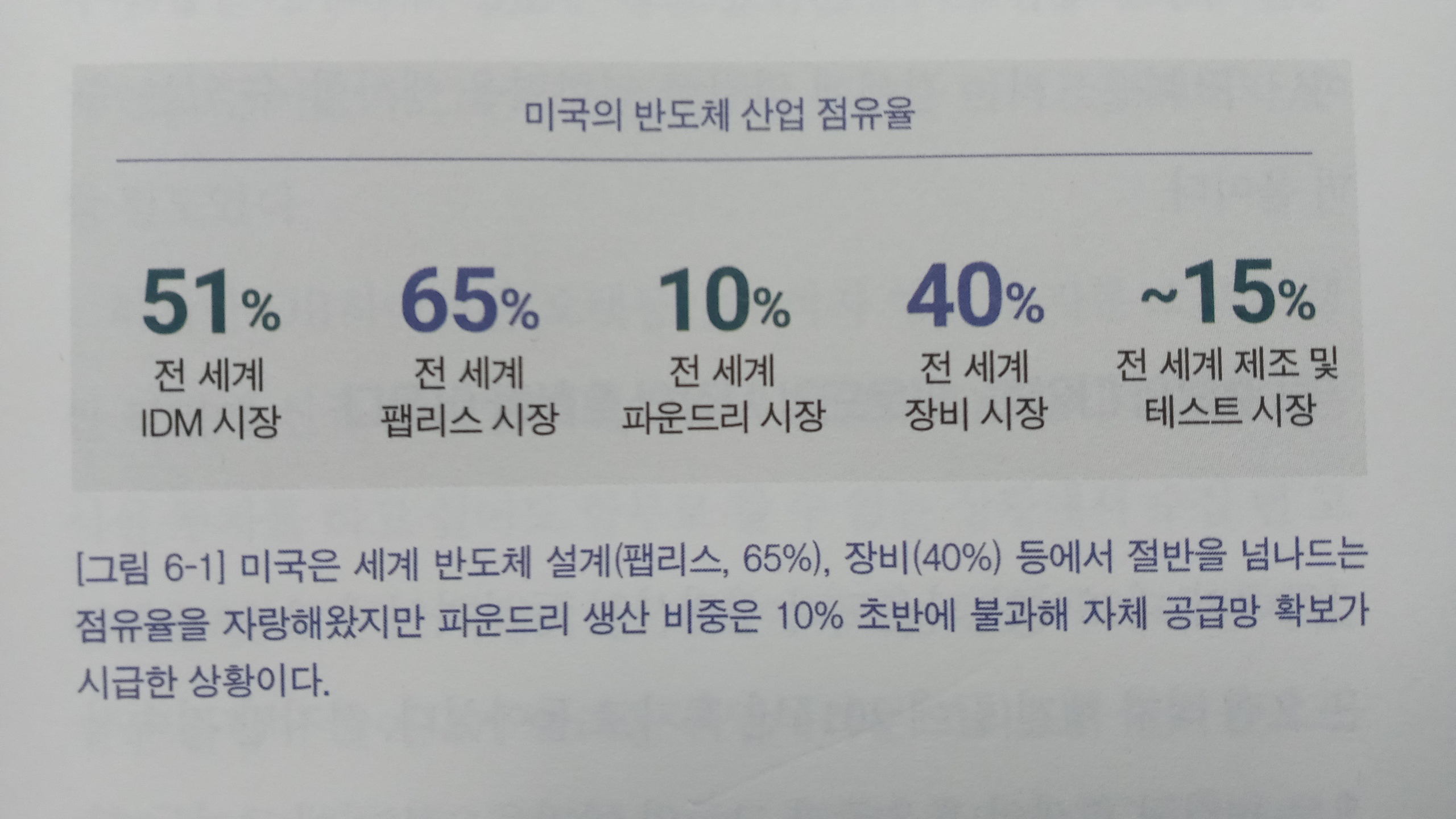

그러나 조금 달리 생각해보면 이처럼 대규모 투자를 집행해야 하므로 다른 기업이 쉽게 끼어들 수 없는 진입 장벽이 형성돼 있는 셈이다. 나름 대규모 투자 집행이 필요하지만 그 규모가 다소 애매한 LED 시장이나 태양광 시장은 시장을 과소평가한 수많 은 경쟁사가 들어올 수 있고, 실제로 과도한 경쟁으로 인해 적자 가 누적된 기업이 차고 넘친다. 그러나 반도체는 이야기가 다르 다. 반도체 중에서 그나마 기술적 진입 장벽이 다소 낮아 경쟁 강 도가 높은 편인 낸드 플래시만 하더라도 매년 수조 원 이상의 설 비 투자가 필요해 태양광 시장처럼 경쟁사가 우후죽순 생길 수 없다. 정신 나간 기업이 아니고서야 시장에 진입할 엄두가 나지 않기 때문이다. 유사 장치 산업인 디스플레이나 2차전지 산업과 비교해도 차원이 다른 규모다. 독보적인 제조 경쟁력을 갖추어야 하는 비메모리반도체 파운드리의 경우는 더욱 심하다. TSMC는 2019년과 2020년 연이어 15조 원대의 설비 투자금 을 집행한 데 이어 2021년에는 더욱 높은 30조원 규모의 설비 투자금을 책정했고, 급기야 2022년에는 설비 투자금을 52조 원까지 늘렸다. 이는 우리나라의 2020년 국방 예산에 달하는 금액이며, 북한의 2020년 GDP보다도 훨씬 높은 수준이다.

- 많은 원소 중 단일 원소로서 현실적으로 반도체에 쓰이는 원소는 단 두 가지뿐이다. 원소기호 14번 실리콘(Si)과 32번 게르마늄(Ge)이 그것이다. 현재의 반도체 산업은 이 중 14번 실리콘을 기반으로 발전해왔다. 게르마늄을 이용한 반도체 칩도 일부 제조되고 있으나, 실리콘은 지구상에 게르마늄보다 풍부하게 존재하므로 가격이 저렴해 반도체를 제조하는 데 가장 많이 사용되어왔다. 또한, 실리콘은 내열 특성이 우수하고 실리콘상에 품질이 좋은 여 러 종류의 물질을 쉽게 형성할 수 있어 각종 칩 구현을 위한 최적의 물질로 꼽힌다.

그러나 과학자들이 고작 두 종류의 반도체에 만족할 리 없다. 두 종류의 물질만으로는 우리가 필요로 하는 다양한 성능의 반도 체 칩과 이에 기반한 전자 부품들을 만들어내기는 어렵기 때문이 다. 따라서 실리콘이나 게르마늄과는 특성이 다른 새로운 반도체 를 발견하고자 꾸준히 많은 연구가 수행되어왔다(물론 여전히 많은 연구가 여전히 진행 중이다!). 단일 원소 중 쓸 만한 반도체 소재는 고 작 실리콘과 게르마늄뿐이므로 더욱 다양한 반도체 소재를 개발 하기 위해 과학자들은 주기율표상의 여러 원소들을 섞어 화합물 (compound)을 만들어내기 시작했고, 이에 따라 여러 종류의 화합 물 반도체가 연구됐다.

- 화합물 반도체는 보통 금속과 비금속이 결합한 구조를 갖는데, 대표적으로 갈륨(Ga)과 비소(As)가 결합한 GaAs나 산화물(oxide) 반도체가 있다. 산화물 반도체는 금속과 산소(O)가 결합한 반도 체 물질인데, 대표적으로는 원소기호 30번 아연(Zn)과 산소가 결 합한 산화아연(ZnO, Zinc Oxide)이 있다. 이외에도 황화물(sulide) 이나 질화물(nitride)을 이용한 반도체 물질 등 여러 반도체 물질이 존재한다.

화합물 반도체 중 기존에 널리 도입되어 산업에 활발히 쓰이는 물질 중 하나로 인듐(In), 갈륨(Ga), 아연(Zn), 산소(O)가 결합한 InGaZnO (인듐갈륨아연산화물, Indium galliun zinx oxid)란 산화물 반도체가 있다. IGZO 라고도 불리는 이 반도체는 특히 디스플레이 산업에서 매우 중요하게 사용된다. IGZO는 픽셀을 껐다 켜는 스 위치를 구현하는 데 사용되는데, 고사양 액정표시장치(LCD) 및 OLED 생산 과정에서 실리콘과 함께 활발히 쓰이고 있다. 특히 IGZO는 소비 전력이 매우 뛰어난 특성을 가져 모바일 기기에 널 리 도입되고 있다. 비록 디스플레이를 구동하는 반도체 중 IGZO 가 사용되는 영역이 극히 일부에 불과해 수혜 강도는 높은 편이 아니나, IGZO 소재를 전문적으로 다루는 국내 상장사인 나노신 소재 같은 기업들에 새로운 시장으로 떠오르고 있다.

IGZO보다 시장에서의 파급 효과가 클 것으로 예상되며 상 용화 준비 단계를 밟고 있는 인듐, 갈륨, 비소(As)가 결합한 InGaAs(인듐갈륨비소, Indium gallium arsenide)와 인듐, 인(P)이 결합한 InP(인화인듐, Indium phosphide) 등의 화합물 반도체도 꾸준히 주목을 받고 있다. InGaAs는 앞 글자를 따 '인가스'라고도 불리는데, 자율주행 시대에 주목받을 반도체 물질로 손꼽히고 있다. 자율주행을 실현하기 위해서는 차량이 실시간으로 주변 환경 을 인지할 수 있어야 하는데, 적외선을 쏴 반사되는 신호를 읽는 LIDAR (Light Detection And Ranging) 시스템은 자율주행의 안정성을 보강하기 위한 필수 요소로, 이를 위해 적외선 신호를 인지하는 적외선 센서가 사용된다. 적외선 물질을 빠르게 감지하는 반도 체로 인가스'라고 불리는 InGaAs, InP 등이 알려지면서 널리 연 구되고 있다. 실리콘은 일부 적외선에 반응하는 특징이 있지만 상온에서는 적외선 감지 특성이 완벽하게 나타나지 않는다. 이는 물 질 고유의 특성에 의한 것으로, 반도체 소재의 종류에 따라 어떤 빛에 반응하는지, 반응 민감도가 어떻게 되는지 등은 상이하다.

- 이처럼 산업의 판도를 바꿀 새로운 반도체 소재의 주인공으로 는 갈륨과 질소가 결합한 GaN (질화갈륨, Gallium nitride), 실리콘과 탄소가 결합한 SiC(탄화규소, Silicon Carbide), 인듐과 인이 결합한 InP 등이 손꼽히고 있다. 이들은 실리콘 소재의 한계를 극복하기 위해 개발된 소재라 포스트 실리콘 소재라 불리기도 한다. 이들 화합물 반도체는 모든 실리콘 반도체를 대체하기 위해 만들어진 게 아니다. 그보다는 일부 전력 반도체나 통신 반도체를 구현하는 과정에서 우수한 특성을 나타내 일부 제품에 널리 쓰일 물질로 꼽 히고 있다. 이들 소재가 실리콘 소재보다 뛰어난 이유는 물질의 고유 값인 밴드갭(band gap)이 실리콘보다 훨씬 큰 와이드 밴드갭 반도체(Wide Band Gap Semiconductor)이기 때문이다.

- 와이드 밴드갭 반도체 소재는 여러 종류가 있다. 실리콘보다 밴드갭이 3배 정도 큰 화합물인 SiC(3.0~3.3eV), GaN (3.4eV)은 이미 반도체 시장의 뜨거운 이슈로 자리 잡았다. eV는 밴드갭의 크기 를 나타내는 단위로 숫자가 클수록 더욱 높은 전압(V)를 버틸 수 있다. SiC, GaN은 두 종류 이상의 원자로 구성되므로 화합물 반도체에 속한다.

밴드갭이 클수록 구속된 전자가 밖으로 자유롭게 빠져나가는 게 더욱 어려워지는데, 이는 높은 전력을 다루거나 고온의 환경에 서 사용되는 전력 반도체에서 특히 중요한 요소다. 3~5V 이내에서 작동하는 칩과 달리 전기차나 전력 설비는 300~1500V 혹은 그 이상 범위에서 작동하는 칩을 요구한다. 게다가 이들 환경은 차량 내부나 산업 현장처럼 높은 온도를 수반한다. 실리콘은 전압이나 온도가 높으면 반도체의 특성이 쉽게 사라진다. 밴드갭이 작은 물질이라서 주변의 에너지로 인해 전자가 너무나 쉽게 원자핵의 구속을 뿌리치고 밖으로 빠져나가기 때문이다. 이를 방지하기 위해 칩을 구성하는 소재의 두께를 늘려 칩을 더욱 두껍게 만드는 등 대안을 고려할 수 있지만, 이는 고내압, 낮은 저항 손실, 고속 스위칭 등 성능이 저하되는 또 다른 결과를 초래한다. 한마디로 하나를 얻으면 하나를 잃어야 하는 트레이드 오프 관계인 것이다.

이에 반해 와이드 밴드갭 반도체는 전자의 전이가 쉽게 발생하 기 어려워 두께가 보다 얇으면서도 높은 전압과 높은 온도의 환 경에서 원활하게 작동한다. 특히, GaN과 SiC는 동일한 구조의 Si 칩보다 무려 10배 이상 높은 전압도 견딜 수 있어 칩 규격에서 1200V급, 3000V급 같은 표현을 쉽게 찾아볼 수 있다. 또한, 칩을 훨씬 얇고 작게 만들어도 Si 칩과 비슷한 수준의 스위치 특성을 구현한다. 발열이 적어 제품 안정성도 뛰어나다. 소재가 갖는 고 유한 특성인 전자 이동도가 높고, 유전율이 기존 반도체 소재보다 낮아 보다 높은 넓은 주파수 대역에서 작동하는 반도체 소자를 수 월하게 구현할 수 있는 장점도 가졌다. 이러한 특성은 반도체 칩 과 함께 탑재되는 부품을 줄여 다양한 반도체 칩을 더욱 수월하게 만들 수 있어 일부 영역에서 서서히 실리콘 반도체를 대체해 나가고 있다. 기업들이 실리콘 반도체에만 집중하던 과거에 와이드 밴드갭 반도체는 국방이나 우주 산업 같은 특수한 영역에 한정적으로 사용되는 반도체로 인식됐다. 제조 기술이 충분히 발달하지 않아 가격이 매우 비싸서 시급한 수요처가 아니면 대부분 실리콘 반도체로 수요를 충당해왔기 때문이다. 그러나 전기차, 신재생에너지 등 새로운 산업이 개화함에 따라 이들 반도체의 수요가 급증하고, 환 경오염을 최소화하기 위해 전력 손실을 가능한 한 줄일 수 있는 방안으로 고효율 반도체 칩의 필요성이 부각되기 시작했다. 앞으 로 더욱 확대될 사물인터넷, 웨어러블 기기와 현재의 모바일 기기 역시 충전 효율을 개선하기 위해 와이드 밴드갭 반도체의 새로운 수요처로 점차 부상하고 있다. 이렇듯 이들 소재의 쓰임새는 기존 영역을 벗어나 꾸준히 확대되고 있다.

- 노트북을 사용하는 사람이라면 이런 생각을 해본 적 있을 것이다. 왜 노트북용 충전기는 크고 무거울까? 스마트폰과 비교할 때 노트북은 충전시 더 높은 출력이 필요하다. 이를 감당하기 위해 서는 전력을 제어하는 반도체 칩과 부품의 크기가 커질 수밖에 없 어 노트북용 충전기는 스마트폰용보다 크고 무겁다. 그런데 GaN 기반 반도체 칩을 사용하면 노트북 충전기의 크기를 스마트폰 충전기 크기로 줄일 수 있어 노트북과 스마트폰을 함께 충전하는 등 고속 충전이 가능해진다. 실제로 앤커 등 일부 기업은 다른 기업들보다 한 발 앞서 GaN 충전기를 선보였으며, 스마트폰 시장의 강자인 애플도 GaN 충전기 도입을 서둘렀다. 애플은 TSMC에 GaN 충전기 제조를 의뢰했는데, TSMC는 자체 GaN 반도체 공 정에 더해 일부 외주를 주는 방식으로 서둘러 GaN 반도체 생산 에 나서 애플의 요구 물량에 맞춰 충전기용 칩을 생산하는 등 시장 확대에 적극적으로 앞서고 있다.

- 전기차와 관련, 와이드 밴드갭 반도체의 중요성은 더욱 커진다. 전기차는 내연기관 차량과 비교할 수 없을 정도로 많은 반도체 칩 과 전장 부품이 탑재된다. 이들 부품에 전력을 전달하는 역할은 전력 반도체가 수행한다. 전기차의 에너지원은 높은 직류 전압을 갖는 배터리뿐인데, 전력 반도체는 직류 배터리 전압을 분배하고 쪼개고 필요에 따라 인버터에 탑재되어 직류와 교류를 변환하는 역할을 함께 맡는다. 내연기관 차량은 연료에서 전기로의 에너지 변환 효율성이 낮고 전력 품질이 떨어져 전장 부품을 탑재하기 어 렵지만, 전기차는 배터리를 사용하므로 훨씬 많은 전장 부품을 탑 재할 수 있다. 이러한 이유로 전장 부품의 전력을 제어하기 위한 전력 반도체의 비중은 차량에 탑재되는 전체 반도체의 20%대에 서 50% 이상으로 급증한다. 그런데 전기차는 더욱 높은 전압 환 경과 혹독한 운행 환경을 감당해내야 하므로 와이드 밴드갭 반도체가 필수적으로 요구된다. 실제로 2015년을 전후해 도요타와 테슬라는 SiC 전력 반도체를 자사 차량에 도입하기 시작했으며, 이후 현대기아차 등 글로벌 자동차 업체들도 뒤따라 이의 연구개발과 도입에 나서기 시작했다.

- 낸드 플래시는 시장 개화가 늦었던 만큼 아직은 기술적 진입 장벽이 상대적으로 낮다. 이에 따라 2021년 초까지도 삼성전자, 키옥시아, 웨스턴디지털, 인텔, 마이크론, SK하이닉스가 6강을 형성하며 시 장을 나눠 가져왔다. 그리고 2021년 말, SK하이닉스가 인텔의 낸드 플래시 사업 부문을 인수하면서 5강으로 재편되기도 했다. 그 러나 메모리반도체의 고용량화에 따라 낸드 플래시의 구조는 더 욱 복잡해지고 제조 기술이 빠르게 발전하면서 진입 장벽이 꾸준히 높아지고 있다. 기술적 장벽이 상대적으로 낮기 때문에 D램제조사보다 낸드 플래시 제조사가 더욱 많은 상황이지만, 향후 기술적 장벽이 꾸준히 높아지고 치킨 게임을 통해 구조조정이 이뤄지면 낸드 플래시도 D램을 따라 과점화가 더욱 공고해질 것이다. 이러한 구조조정 속에서 낸드 플래시 메이커가 도태되거나 인수되어 줄어든다면, 이는 곧 살아남는 메이커는 과점화를 바탕으로 수익성 향상을 누리게 됨을 의미한다. 이는 주식시장에서도 더욱 긍정적인 평가를 받는 요인이 될 것이다.

- D램은 휘발성 메모리를 대표하는 제품으로 자리 잡으면서 국내 반도체 산업을 이끌었다. 데이터가 저장되는 모든 공간에는 D램이 사용된다고 말해도 과언이 아니다. 컴퓨터, 노트북, 스마트 폰 외에 대규모 데이터를 저장하는 데이터센터나 클라우드는 물론, 많은 양의 데이터를 처리하는 그래픽카드나 차량용 반도체에도 D램이 반드시 탑재된다. 어디에 사용되는 데이터를 영구적으로 저장하는 비휘발성 메모리는 속도가 느리므로 연산장치로 가는 길목에는 반드시 속도가 빠른 D램이 필요하기 때문이다. 현대 컴퓨터의 주기억장치는 D램이 표준이다. 그런데 D램보다 더욱 빠른 성능을 자랑하는 메모리반도체인 S램도 있다. S램은 심지어 D램보다 소비 전력도 낮다. 하지만 S램은 데이터를 저 장하려면 6개나 되는 트랜지스터가 래치(Latch) 형태로 모여 작동해야 한다. 이에 반해 D램은 스위치 기능을 하는 트랜지스터 1개와 데이터를 저장하는 캐패시터(Capacitor) 1개로 구성되어 있어 S 램보다 구조가 월등히 단순하다. S램은 구조가 복잡하다 보니 당연히 많은 공간이 필요한데, 이는 반도체 업체들이 칩 용량을 늘 리는 과정에서 심각한 문제가 된다. 용량 대비 가격도 D램보다 현저히 높아 경쟁력이 떨어진다. 아무리 속도가 중요하다고 해도 가격이 받쳐주지 않으면 대중화되는 데 한계가 있을 수밖에 없다. 이는 반도체 칩을 만드는 데 있어 성능뿐만 아니라 시장성과 양 산성도 매우 중요하다는 사실을 보여준다. 어찌 됐든 이런 이유로 고용량 휘발성 메모리는 S램이 아닌 D램을 중심으로 대중화됐다.

- 휘발성 메모리반도체 시장은 D램이 주도하고 있지만, S램 역시 알게 모르게 널리 쓰이고 있다. 컴퓨터와 스마트폰의 연산장치인 CPU에는 기본적으로 S램이 내장된다. 연산장치는 다음 연산 시 입력되어야 할 데이터를 휘발성 메모리에 저장한다. 연산장치 초기 시절에는 이런 메모리가 1개의 메모리 칩으로 단순하게 이루어져 있었다. 그러나 1980년대 들어 연산장치의 성능이 점차 발달하면서 데이터 처리 속도가 매우 빨라졌다. 이에 따라 메모리의 데이터 처리 속도와 격차가 더욱 벌어졌고, 이를 극복하기 위해 메모리 구조도 복잡해졌다. 이 과정에서 고성능 CPU는 물론 저성능 연산 칩까지도 여러 개의 휘발성 메모리를 이용했다. 이들 휘발성 메모리는 연산장치 가장 가까이에서 데이터를 처리하는 메모리부터 가장 멀리 떨어져 있는 메모리 순으로 계층적인 구조 를 갖는다. 흔히 연산장치로부터 가까운 순서로 L1, L2, L3 캐시 라 부르며, 필요에 따라 L0 캐시가 사용되기도 한다.

- 일반적으로, CPU와 가장 가까운 캐시는 D램이 아닌 S램이 담당한다. D램은 IT 기술이 발달함에 따라 꾸준히 용량이 증가해왔다. 그러나 S램보다 속도가 느리다는 태생적인 한계가 있다. 또한 용량이 커 CPU가 데이터를 읽기 위해 너무 많은 구역을 탐색해야 하는 문제점도 있다. 따라서 CPU와 메모리의 데이터 처리 속 도 격차를 최소화하기 위해 더욱 속도가 빠르고 용량이 작고 계 층적 구조를 가진 S램이 CPU 부근에 함께 탑재되기 시작했다. S램은 주로 CPU 제조사들이 CPU를 제조하는 과정에 함께 설계해 CPU와 함께 제조하는데, CPU 제조사들은 CPU의 연산 속도를 높이려는 경쟁을 벌이는 것 외에도 S램의 성능을 향상시키려 는 경쟁을 물밑에서 펼치고 있다. 내 컴퓨터의 CPU가 어느 정도 의 캐시 메모리를 이용하는지는 윈도 내 작업관리자를 통해 확인 할 수 있다.

- 2020년 반도체 시장을 달군 이슈가 있었다. 바로 DDR5의 도입이다. DDR4는 2012년 표준이 정해졌고, 이후 점진적으로 도 입됐다. DDR4의 뒤를 잇는 DDR5는 2020년 7월 표준이 정해졌 다. 새로운 DDR 표준이 정해지면 D램 제조업체들은 점진적으 로 새로운 규격의 제품 생산을 확대한다. 표준이 정해진 첫해에는 기술력을 과시하기 위한 시제품 중심으로 생산되나, 다음 해에는 서버용 등 고사양 제품의 비중이 늘어나기 시작한다. 2년쯤 지나 면 일반 PC용 제품까지 범위가 확대되면서 새로운 규격의 비중 이 점점 높아지는데, 이때부터 일반 소비자들은 적극적으로 D램 을 교체하기 시작한다. 표준으로 확정된 이후 4~5년 지나면 비로 소 기존 DDR 제품보다 새로운 규격의 DDR 제품의 생산 비중이 늘어나는 경향이 나타났다.

새로운 규격의 제품은 출시된 직후에는 가격이 매우 비싸다. D 램 업체들은 막대한 투자 비용을 빠르게 회수하고 싶게 마련인데, 초기 단계에는 수율이 낮고 생산 물량이 많지 않은 반면, 고사양 시장을 중심으로 수요가 먼저 발생하므로 신제품을 높은 가격에 출시해도 비교적 수월하게 판매할 수 있다. 그러나 언제까지나 고 사양 시장 중심으로만 제품을 판매할 수는 없다. 일반 PC 시장까지 시장을 확대해야 한다. 다행히 생산이 거듭될수록 수율이 증가하고 제조 공정이 안정되면서 생산 단가가 떨어진다. 또한, D 램규격이 바뀌면 CPU도 새로운 규격의 D램과 호환되어야 하는데, 새로운 규격이 확립된 뒤 2년쯤 지나면 새로운 D램을 지원하는 CPU도 활발히 출시되기 시작한다. 이때부터 일반 소비자용 수요 와 공급이 증가하기 시작한다.

DDR의 성능은 세대가 바뀔 때만 향상되는 게 아니다. USB도 3.0, 3.1, 3.2를 거쳐 4.0이 나오고 4G 통신도 LTE와 LTE-A를 거 쳐 5G로 가듯, DDR도 DDR4 내에서, DDR5 내에서 꾸준히 성 능 개선이 이루어진다. 미세한 발전이 거듭되면서 칩 제조에 사용되는 소재의 종류도 조금씩 변한다. 그러나 급격한 변화는 세대가 변할 때 집중적으로 일어난다(새로운 투자 기회도 단연 이때 많이 발생한다!). 규격이 변경됨에 따라 칩과 모듈의 외형이 바뀌고 작동 방식이 변경되기 때문이다. 칩을 지지하는 패키지 기판과 RAM 모 듈의 PCB도 함께 변하므로, 심텍 같은 기판 제조사들은 새로운 규격에 대응해 보다 고수익성 제품을 출시해야 한다. 이러한 이유로 세대가 지난 RAM은 신형 컴퓨터에 부착되지 않는다. 규격이 변경되면 제조 공정에 사용되는 일부 장비의 교체도 필 연적인데, D램은 설비 투자 규모가 크고 생산 주기가 비교적 길어 생산 설비 중 다수가 세대 변화에 따라 교체되는 경향이 있다. 특히, 칩 외형이 크게 변해서 후공정 단계에서는 장비 교체가 더욱 활발히 일어나는데, 이 과정에서 추가로 필요한 생산 장비나 부품이 생기기도 한다. DDR5는 DDR4보다 동작 전압이 낮아 PC 메인보드에서 전력을 받는 과정에서 데이터 처리 오류가 발 생했는데, 전력 관리 칩을 RAM의 PCB에 부착해서 해결했다. 또한 전력 칩에서 분배되는 전기 신호는 반드시 잡음이 섞이기 마련 인데, 이를 최소화하기 위해 필수적으로 캐패시터와 인덕터 같은 수동 부품이 추가로 사용됐다.

- 낸드 플래시는 전자를 가둬 데이터를 저장하는데, D램 캐패시터와 달리 전자가 빠져나갈 수 없는 비휘발성 메모리반도체다. 이렇게 전자가 저장되는 공간을 셀(cell)이라고 한다. 데이터를 영구 저장하는 또 다른 메모리반도체로 노어 플래시가 있다. 낸드 플래 시와 노어 플래시를 가리켜 플래시메모리라 한다.

낸드 플래시는 전자가 저장되는 여러 셀이 모두 하나의 세트처럼 작동하는 직렬 구조를 가졌지만, 노어 플래시는 개별 셀이 모두 따로따로 마련되어 있어 병렬로 작동한다. 따라서 낸드 플래시는 특정한 셀의 데이터를 읽으려면 여러 셀에 동시에 전기 신호를 가해 순차적으로 데이터를 읽어들여야 한다. 슈퍼마켓의 냉동고에서 내가 원하는 아이스크림만 딱 선택해서 꺼내는 것이 아니라, 아이스크림을 한가득 꺼낸 뒤 마음에 드는 것을 고르고 나머지는 다시 넣어두는 것과 같다. 이는 데이터 읽기 속도가 느려지는 이유가 된다. 반면, 노어 플래시는 특정한 셀을 정확히 지정해 신호 를 인가해 데이터를 읽고 쓰므로 원하는 데이터만 빠르게 읽어낼 수 있다. 그래서 전문가가 아닌 입장에서 보면 단연 노어 플래시 가 더욱 좋은 플래시메모리처럼 보일 수 있다.

그런데 낸드 플래시는 노어 플래시보다 전기 신호가 오가는 배 선의 수가 획기적으로 적다. 낸드 플래시는 1개의 배선으로 여러 셀에 신호를 전달하는 반면, 노어 플래시는 모든 셀에 일일이 별도 의 배선을 만들어야 한다. 낸드 플래시는 집적도 면에서 유리해 용 량 극대화가 가능하다. 용량 극대화를 중시하는 시장의 수요를 간파한 삼성전자와 도시바가 노어 플래시 진영을 꺾고 플래시메모리 시장을 주도하게 된 이유다.

- 2000년 전후만 해도 플래시메모리 시장을 낸드 플래시가 앞서 나가리라 예측하기는 어려웠다. 2000년대 초에 출시된 핸드폰의 90% 이상에는 노어 플래시가 탑재되어 있었는데, 인텔, AMD와 후지쓰의 합작사인 스팬션, 스위스의 ST마이크로가 노어 플래 시 시장을 주도하고 있었다. 이들 노어 플래시 진영 역시 낸드 플 래시가 위협적인 경쟁 제품이라 판단했지만 당시 상용화된 낸드 플래시 제품의 수명이 매우 짧아 주류가 되지는 못할 것이라 판단했다.

그러나 속도라는 장점보다 용량 극대화에 대한 시장의 요구는 생각보다 거셌다. 게다가 낸드 플래시의 짧은 수명은 기술 발전뿐 만이 아니라 용량 극대화를 통해서도 개선됐다. 셀의 수명은 데이 터의 쓰기 및 지우기 횟수에 의해 결정된다. 그런데 낸드 플래시 의 용량이 커지면서 데이터가 더욱 많은 셀에 분산 저장되어 셀당 쓰기 및 지우기 횟수가 감소하므로 실질적인 수명 증가 효과가 나 타났다. 집적도 극대화를 바탕으로 용량이 크게 늘어나면서 수명 에 대한 우려가 자연스레 해소된 것이다. 낸드 플래시가 더욱 큰 용량으로 손쉽게 무장하고 수명 향상까지 이루어내자 노어 플래시가 설 자리는 빠르게 사라졌다. 결국 낸드 플래시는 플래시메모리 시장을 지배하게 되었고, 노어 플래시 진영은 사실상 메모리반 도체 시장에서 자취를 감추게 되었다.

- 플래시메모리는 데이터 삭제 속도가 느리다. 플래시메모리는 전자를 격벽 구조 또는 푸딩 구조에 구속해 데이터를 저장하는데, 전자를 다시 빼내는 과정에서 마이크로초(us)~밀리초(s) 수준의 시간이 소요된다. 안 그래도 삭제 속도가 느린데, 때로는 새로운 데이터를 작성하기 위해 기존에 쓰여 있던 불필요한 데이터를 삭 제하는 작업을 함께 해주어야 하는 경우도 생긴다. 이처럼 기존 데이터 위에 새 데이터를 덮어쓰는 데 너무 오랜 시간이 소요된 다. 따라서 새로운 데이터가 들어오기 전, 일정한 주기마다 여러 셀의 데이터를 바이트 또는 페이지 단위로 한 번에 미리 삭제하는 방식이 사용되고 있다.

이는 데이터 관리를 아주 복잡하게 만든다. 1번 페이지의 일부 데이터를 삭제하고 싶어도 해당 데이터만 선택적으로 삭제할 수 없다. 나머지 삭제하지 않을 데이터를 다른 페이지에 복사한 뒤, 1번 페이지를 통째로 날려야 한다. 낸드 플래시에 기반한 저장장 치는 하드디스크와 달리 디스크 조각모음을 사용하지 않으며, 주 기적으로 메모리 내 특정 구역을 비우는 트림 작업을 수행한다.

- 낸드 플래시와 노어 플래시는 모두 도시바가 제안한 개념이나, 노어 플래시는 인텔에 의해 1988년에, 낸드 플래시는 도시바에 의해 1989년에 최초로 상용화됐다.8 이후 낸드 플래시는 전자기 기의 핵심 저장장치로 자리 잡았다. 이에 반해 노어 플래시는 집 적도 향상의 어려움과 비싼 가격으로 인해 일부 임베디드 시스템 을 중심으로 제한적으로 사용됐다. 낸드 플래시는 도시바의 주도 아래 시장이 만들어졌으나, 이후 D램 등을 생산하면서 풍부한 경 험을 쌓고 설비 자산을 갖춘 삼성전자가 도시바를 앞지르며 낸드 플래시 기술 발전을 주도했다.

낸드 플래시는 구조가 단순하다는 특징과 고유의 동작 방식을 바탕으로 셀을 수직으로 적층해서 용량을 극대화하는 3D 낸드로 발전했다. 단층 건물에서 고층 빌딩으로 건축물이 높아지면서 주거 공간이 늘어나는 것과 비슷하다고 생각하면 된다. 웨이퍼상에 미세한 칩을 만드는 것보다 수직으로 많이 쌓는 기업이 원가 절감에 더욱 유리해지면서 승기를 잡는 구도가 된 것이다. 3D 낸드 제조를 위해서는 장비와 소재 기술의 발달이 필수적인데, 층수가 증가하면서 장비와 소재 기술도 매우 빠르게 발전했다. 이와 관련, 램리서치는 타사의 추종을 불허하는 장비를 개발했고, 솔브레인 과 엘티씨에이엠은 새로운 식각 소재에서 성장 동력을 찾기도 했다. 3D 낸드로의 구조 변화로 수혜를 입는 새로운 기업들이 다수 나타난 것이다.

- 3D 낸드에 이어 4D 낸드도 등장했는데, 4D 낸드는 근본적으로 3D 낸드와 크게 다르지 않으나, 기존 3D 낸드가 칩 내부의 신호 처리를 위한 각종 회로(peri)를 칩 내 별도의 공간에 만들어 공 간을 소모했던 것과 달리 전자가 저장되는 셀들이 위치한 공간의 하단부에 만들어 공간을 절약한 형태다. 오래된 아파트는 주차 공간이 외부에 위치하지만 최신 아파트는 주차장을 지하에 설치해 공간을 더욱 절약하는 경우와 마찬가지다.

- SSD는 낸드 플래시에 기반한 저장장치다. 낸드 플래시가 데이 터 저장이라는 핵심적인 역할을 맡되, 데이터 저장 알고리즘을 처리하는 컨트롤러 칩과 캐시 메모리용 D램, 그리고 여러 수동 부품이 함께 PCB에 실장되어 최종적으로 SSD라는 완제품을 구성한다. 하드디스크는 여전히 관련 기술이 발전할 여지가 남아 있으나 SSD의 기술 발전과 가격 하락 속도가 워낙 빨라 하드디스크가 자취를 감추기까지는 시간이 그리 오래 걸리지 않을 것으로 보인다.

- 모바일 기기 시장에 이어 컴퓨터 시장에도 SSD가 도입되면서 윈도 부팅 시간이 대폭 줄어들고 파일 실행 속도나 로딩 속도가 급격히 빨라지는 등 전반적인 동작 속도가 크게 개선됐다. 하드디스크로는 구현할 수 없는 놀라운 성능이었다. 특히 노트북 시장에선 상상할 수 없었던 애플 맥북, LG 그램 같은 경량 노트북이 출시될 수 있었다. SSD는 초기에는 2.5인치 정도의 크기였으나, 기술 발전으로 다양한 형태의 SSD가 출시되면서 PC용으로는 손가 락 길이의 M2 SSD가 노트북용으로는 동전만 한 BGA SSD가 등장했다.

SSD는 낸드 플래시에 기반하기 때문에 하드디스크보다 수명 이 짧다는 한계가 있다. 그래서 중요한 데이터는 하드디스크에 병 행 보관해야 한다는 인식이 지배적이었다. 짧은 수명뿐만 아니라 빠른 성능 향상으로 인해 제품의 교체 주기가 하드디스크보다 현 저히 짧다. 이러한 교체 수요는 낸드 플래시 시장의 성장을 이끄는 주요 요인이다.

SSD는 2010년대 들어 널리 쓰이기 시작했다. 64GB SSD가 보편화되고 몇 년 지나지 않아 TB 단위의 SSD도 등장했다. 64GB SSD가 출시됐을 무렵, SSD는 운영체제와 가장 중요한 일부 프로 그램만 설치하는 용도로 사용됐으나 이제는 모든 파일을 저장하 는 보편적인 저장장치로 자리 잡았다. 막대한 양의 데이터를 보관 하는 서버 시장도 SSD를 적극적으로 도입하며 SSD 시장의 큰 축이 됐다.

- 인텔이 공개한 크로스포인트 메모리는 스위치 기능을 하는 셀렉터 (selector)와 0과 1데이터를 저장하는 메모리 셀로 구성된다. 데이터를 저장하고 삭 제하기 위해 두 종류의 서로 다른 전기 신호가 십자 모양으로 교 차되는 배선이 각 셀에 장착되어 이들 셀에 전달된다. 인텔의 신 제품을 소개하는 기사에서는 신제품이 낸드 플래시보다 1000배 나 빠르다고 강조했으나, 이는 전반적인 동작 속도가 아닌 신호가 데이터에 접근하는 과정에서 발생하는 신호 지연의 차이가 1000 배라는 의미로, 실제 구동 속도는 현존하는 SSD와 큰 차이를 느끼기 어려운 정도였다. 그럼에도 불구하고 SSD 보다 조금이라도 빠르다면 충분히 차세대 메모리반도체로 고려해봄 직하니 크로스포인트 메모리가 위협적인 경쟁 상대가 될 수도 있었다.

그러나 크로스포인트 메모리는 치명적인 단점이 있었다. 바로 시장성을 유지하면서 용량을 늘리기가 쉽지 않다는 점이었다. 낸 드 플래시는 3D 낸드 플래시 형태로 발전했고, 층수는 해가 다르 게 꾸준히 증가했다. 이에 반해 인텔이 처음 소개한 크로스포인 트 메모리는 단층 또는 2층 구조를 가졌으며, 용량을 극대화하기 위해서는 낸드 플래시와 마찬가지로 층수를 보다 크게 늘려야 했다. 셀렉터, 메모리 셀, 금속 배선을 연이어 한 층 한 층 쌓아 올리 며 만들어야 하는데, 크로스포인트 메모리는 공정 난이도가 상당할 뿐만 아니라 각 층을 쌓아 올릴 때마다 잦은 미세 식각과 원자플 래시는 층수가 증가해도 공정 수가 층 수에 비례해 증가하지 않 으므로 층수 증가에 따른 용량당 단가가 크게 절감되는 이점이 있는 반면, 크로스포인트 메모리는 용량이 증가하면 생산 원가도 함께 증가하므로 낸드 플래시 같은 원가 절감이 어려웠다. 따라서 고용량이 무엇보다 중요한 의미를 갖는 현재의 시장에서 낸드 플래시와 직접적으로 경쟁하기 어려울 수밖에 없었다. 아무리 좋은 반도체라도 가격 경쟁력이 없으면 현실적으로 시장성이 없는 것이다. 이러한 이유로 인텔은 크로스포인트 메모리를 낸드 플래시의 경쟁 상품이라기보다는 운영체제 구동 같은 영역에서 한정적으로 PC 또는 서버의 성능을 개선하는 틈새시장형 제품으로 소개했다.

- D램이 0과 1 데이터의 저장을 위해 캐패시터를 사용하는 것과 달리 인텔의 크로스포인트 메모리는 메모리 셀 소재로 PCM을 선택했다. PCM은 전기 신호를 가하면 물질의 상(phase)이 변하는 상변화 소재에 기반하는데, 전압을 가하면 원자들이 재배열되며, 결정 상태가 변하는 원리를 따른다. PCM은 흔히 P램이라고도 불 리는데, D램과 낸드 플래시를 대체할 차세대 반도체 소재로 꾸준 히 연구되어왔다. 삼성전자도 2004년 세계 최초로 P램을 개발해 피처폰에 탑재한 경험이 있다. 그러나 P램은 양산 공정의 어려움과 기존 메모리반도체의 지속적인 발달로 여전히 연구개발 단계에 머물러 있다.

이외에 물질의 자성을 이용한 M램도 차세대 반도체로 빈번히 언급되고 있다. 이러한 연구에도 불구하고 차세대 메모리반도체 의 등장이 자꾸만 늦춰지는 근본적인 이유로는 현저히 낮은 생산성, 미세화의 어려움, 수직 구조 형성을 통한 용량 극대화의 어려 움, 높은 생산 비용, 그리고 기존 기술의 빠른 발전 등을 꼽을 수 있다. 낸드 플래시는 수직으로 끊임없이 셀을 쌓아가며 용량을 증 가시키고, 하나의 셀에 전기적 신호를 쪼개 인가하는 TLC, QLC 등을 통해 1개 셀에 최대 2~4자릿수 이상의 데이터를 입력하며 용량을 추가적으로 극대화시켰다. D램은 지속적인 미세화와 캐 패시터 기술의 발달로 꾸준히 세대를 연장하며 고속 고용량 메모리반도체 시장에서 선두 지위를 유지하고 있다. 낸드 플래시는 층수를 더욱 증가시킬 수 있는 기술들이 꾸준히 발표되고 있다. D 램 또한 미세화가 꾸준히 이루어지면서도 3D D램 등 새로운 구 조가 제시되고 있다. 이에 더해 패키지 칩의 적층 방식 등을 통해 성능이 꾸준히 향상되고 있다.

이처럼 격차가 날로 줄기 어려우므로 차세대 메모리반도체는 기존 메모리반도체를 빠르게 대체하기보다는 먼저 틈새시장 공략에 나설 가능성이 크다. 이 과정에서 가장 중요한 전제는 칩을 제조할 장비와 소재가 먼저 개발되어야 한다는 것이다. 실제로 어플라이드 머티리얼즈 등 글로벌 장비 제조사들은 시장성이 낮은데도 불구하고 꾸준히 차세대 메모리반도체용 장비를 출시하며 시장이 만들어지기를 기다려왔다. 반도체 업체들은 이들 장비를 구매해 차세대 반도체 개발에 사용하고 있다. 비록 시장이 만들어지는데 오랜 시간이 걸릴 것으로 보이나, 메모리 패러다임의 변화는 장비는 물론 소재 기술에도 점진적으로 커다란 변화를 가져올 것이므로 노련한 투자자라면 관련 기술이 어떻게 변해가는지 관찰해볼 필요가 있다.

- MCU는 쉽게 생각하면 성능이 아주 낮은 CPU라고 볼 수 있으며, 초소형 컴퓨터라고 불리기도 한다. 입력 신호가 들어오면 정해진 절차에 따라 연산을 통해 신호를 처리한 뒤 그 결팟값을 전자기기에 출력하는데, 그 과정에서 컴퓨터와 비슷한 역할을 하기 때문이다. MCU는 입력 신호가 들어오면 어떤 명령을 수행할지 명령어가 미리 짜여 있는데, 명령어를 저장해두기 위해 비휘발성 메모리인 ROM이 탑재돼 있다. 주로 플래시메모리가 이용되는 데, 비휘발성 메모리는 읽기 속도가 느리므로 RAM도 함께 탑재 된다. | MCU는 연산 기능을 수행하는 CPU와 RAM, ROM으로 구성 된다. CPU가 한번에 얼마나 많은 데이터를 처리할 수 있는가에 따라 MCU의 종류는 8비트, 16비트, 32비트 등으로 나뉜다. 숫자가 높을수록 한번에 처리할 수 있는 명령어의 길이가 길어진다. 더욱 복잡한 연산을 수행하기 위해서는 비트 수가 높은 MCU가 필요한데, 비트 수가 증가함에 따라 칩 설계 기술력과 함께 단가도 높아진다. 칩의 집적도도 함께 고도화된다. MCU 시장은 과거 4비트, 8비트가 중심이었으나 16비트, 32비트 MCU 사용이 꾸준 히 늘고 있다. MCU는 모든 전자제품에 폭넓게 사용되고 있다. TV용 MCU 는 신호가 들어오면 영상을 녹화하도록 명령을 내리거나 채널을 바꿔주며, 리모컨용 MCU는 어떤 버튼을 누르면 어떤 신호를 송 출할지 정해진 프로그램에 따라 신호를 출력한다. 시계에도 정밀한 시간 측정과 표시를 위해 MCU가 사용된다. MCU가 사용되 지 않는 전자제품은 사실상 없다고 할 수 있다.

- LG전자는 가전제품을 제조하는 과정에서 수많은 MCU가 필요하나, 이의 공급을 도시바, 파나소닉 등 일 본 기업들에 의존해왔다. 그러다 1999년 MCU의 국산화와 계열 사의 자체 공급을 확대하기 위해 계열사 실리콘웍스(현 LX세미콘) 가 MCU 시장에 진입했다. 비록 사업 초기이고 해외 제품의 가격 경쟁력을 무시할 수 없어 만만한 영역은 아니지만, LG그룹을 등 에 업고 사양이 낮은 제품부터 차츰 공급을 확대하면 향후 고성능 MCU 시장도 노릴 수 있을 것으로 기대된다. MCU는 사용처와 종류가 다양해 일일이 나열하기 어렵다. 이는 그만큼 다품종 맞춤 생산이 중요한 영역임을 의미한다. 이런 이유로 MCU 전문 기업들은 고객사의 단가 인하 압력이 다른 전자 부품에 비해 적거나 전사 이익 변동성이 낮은 특징이 있다. 상장사 어보브반도체도 이에 해당하는 사례다.

- 초기 스마트폰은 PC만큼 사양이 높을 필요가 없었다. AP는 성능보다 전력 소비를 낮추는 데 집중했다. 그러다 보니 CPU는 PC용으로, AP는 모바일 기기용으로 명확히 구분됐다. 그러나 AP는 예상보다 빨리 발전했다. 설계 기술과 집적화의 발달로 AP는 저전력을 유지하면서도 고성능을 실현 할 수 있게 되었다. 그러는 와중, 태블릿 PC라 불리는, 노트북을 흉내 내는 제품이 탄생했다. 이 같은 외부 변수에 힘입어 AP의 성 장세는 멈추지 않았다. 결국 이제는 태블릿을 넘어 노트북과 컴퓨 터에까지 AP를 탑재하는 시대가 됐다. 삼성전자가 2019년 출시한 갤럭시 북S 퀄컴(Qualcomm)이 대표적인 사례다.

기존에는 컴퓨터를 살 때 CPU나 그래픽카드의 성능을 중점적 으로 살펴봤지만, 이제는 CPU 대신 AP가 탑재된 제품은 어떤지 함께 살펴봐야 하는 시대가 되었다. AP가 CPU의 영역을 넘보기에는 여전히 성능의 격차가 존재하지만, AP는 저전력이라는 장점과 성능 향상을 바탕으로 PC 시장의 전유물을 대체하기 위해 지속적으로 도전할 것이다. 이에 반해 CPU 또한 우수한 성능을 내세우며 더욱 앞서가고자 노력할 것이다.

- 동운아나텍은 핸드폰의 각종 기능을 동작시키는 데 필수적인 스마트폰용 드라이버 IC를 전문적으로 설계하는 회사다. 주력 사 업은 카메라에 사용되는 AF (Auto Focus) 및 OIS용 드라이버 IC며, 이외에도 디스플레이의 전력을 제어하는 IC, 햅틱 IC 등을 설계해 스마트폰 제조사를 중심으로 제품을 공급하고 있다. 동운아나텍 은 이들 칩의 설계를 담당하며, 삼성전자나 매그나칩반도체 같은 파운드리나 네패스, JECT 같은 후공정 업체에 제조를 의뢰한다. 동운아나텍은 현재 스마트폰에 평준화되어 있는 기능을 구현하기 위한 제품을 공급하고 있어서 비교적 광범위한 종류의 스마트 폰을 대상으로 시장이 형성돼 있다. 주로 삼성전자 및 중국을 중심 으로 제품을 공급하고 있으며, 제품의 수명 주기가 상대적으로 짧은 편이다. 겉으로 보기에는 모든 스마트폰이 동일한 OIS 기능을 탑재한 것 같지만 스마트폰의 제품 종류와 출시 시기에 따라 액추에이터의 구동 기술도 오픈 루프(Open Loop), 클로즈 루프(Closed Loop), 폴디드 줌(Folded Zoom) 등으로 점차 변하기 때문이다. 이러한 기술 변화에 따라 새로운 드라이버 IC가 필요해진다. 동운아나텍은 이 같은 변화에 맞춰 고객사가 요구할 것으로 예상되는 드라이버 IC를 한 발 앞서 개발해내야 한다. 기술 변화가 비교적 빠르게 일어나므로 지속적인 신제품 개발력이 곧 장기 성과와 직결될 가 능성이 크다. 만약 개발에 실패할 경우 소수 제품군에서 상당수의 매출이 나오는 만큼 기업의 존재가 위태로울 수 있다. 앞서 어보브 반도체가 다양한 제품을 고루 오래 파는 것과 상당히 대조적이다. 투자자는 이처럼 똑같이 팹리스라 불리는 기업들이라도, 기업들의 상세 비즈니스 모델이 전혀 다름을 이해해야 한다.

동운아나텍은 지속적인 제품 개발 레퍼런스(reference, 납품 경험 혹은 납품 기록)를 바탕으로 국내 AF 및 OIS 드라이버 IC 1위 업체라는 명성을 차지하고 있으며, 미국의 ON 세미컨덕터와 일본의 아 사히 카세이 같은 세계적 기업들과 경쟁 구도를 형성하고 있다.

- 얼핏 보면 ARM이나 시놉시스는 제품을 만들지도 않고 앉아서 특허료만 먹는 기업처럼 보일지도 모른다. 그러나 이는 무형 자산에 대한 개념이 없어서 만들어진 잘못된 생각이다. ARM과 시놉시스는 IP 개발을 위해 끊임없이 막대한 투자를 하고 있다. 이 들 기업이 존재하지 않는다면 전 세계 팹리스들의 칩 개발 속도는 현저히 느려져 기술 발전이 정체될 것이다. 게다가 이런 기업들이 존재하지 않는다면 팹리스가 칩을 처음부터 끝까지 모두 설계해 야 하므로 막대한 비용 및 시간 투자가 필요해 반도체 칩 가격은 폭등할 것이다. 칩 개발에 오랜 시간이 걸려 인류 문명의 발달 속 도도 지연될 것이다. 그만큼 IP 전문 기업의 역할과 산업 기여도는 막대하다.

- ARM의 IP는 현재 출시된 대부분 스마트폰에 사용될 정도로 전 세계적으로 사용 빈도가 높다. 이에 비해 규모는 작더라도 전문적인 영역에서 IP 경쟁력을 갖고 있는 기업들도 있다. 국내 상 장사 칩스앤미디어는 팹리스로 분류되지만, 완성된 칩을 설계하 지 않고 IP 라이선스 판매 사업에 주력한다. 칩스앤미디어의 주력 사업 영역은 비디오 영상 처리다. 스마트폰이나 TV는 물론 차량 등의 보안카메라는 고화질 영상을 촬영한 뒤 영상 처리 과정을 거쳐야 하는데, 칩스앤미디어는 이 과정에서 사용되는 영상 처리 IP를 집중적으로 개발해왔다. 영상을 처리하는 과정에서 연산장치는 복잡한 연산을 수행하고 소프트웨어가 추가로 보정 작업을 진행하는데, 칩스앤미디어는 두 영역 모두에 걸쳐 효율적인 영상 처리를 가능하게 해주는 IP를 개발했다.

칩스앤미디어의 IP 개발은 주로 네덜란드의 NXP 같은 전방 고객사의 수요에 의해 시작되는데, 전방 고객사가 IP를 적용해 제품 개발을 마친 뒤 판매가 시작되면 칩스앤미디어 같은 IP 개발 기업의 로열티 매출이 추가로 발생하므로 고객사의 제품 판매는 이 기업의 외형 확대에 중요한 변수가 된다.

- ARM은 2010년부터 서버용 아키텍처를 출시했으나 시장에서의 존재감은 미미했다. 서버 시장이 고성능 CPU를 우선하다 보니 저전력보다 성능에 강점을 둔 인텔의 x86 아키텍처가 승승장구했다. 실제로 ARM은 2020년이 저물어갈 때까지 서버 시장 점유율이 0%대일 정도로, 부끄러운 수치를 기록해왔다. 그런데도 ARM의 서버 시장 내 지위가 확대될 것이라는 전망이 제시되면 서 경쟁사들은 두려움을 감추지 못하고 있다. 서버 시장은 매우 보수적이어서 아키텍처 변화를 받아들이는 데 소극적인 모습을 나타내는데도 말이다.

이 같은 배경에는 ARM IP의 성능이 꾸준히 향상되고 있으며 전력 효율성이 뛰어나다는 막강한 장점이 큰 영향을 미쳤다. ARM의 서버 시장 침투는 모바일 기기 시장에서 쌓은 노하우를 바탕으로 한다. 와트당 더욱 많은 연산을 제공한다는 것은 곧 가 성비가 뛰어남을 의미한다. 실제로 고성능에 집중하고 있는 현재 의 서버는 점차 가성비를 향해 움직일 것으로 전망된다. 2020년 대 들어 세계 최대의 클라우드 업체인 아마존과 마이크로소프트 는 전력 소모가 큰 인텔의 CPU에서 벗어나 ARM의 IP에 기반한 자체 저전력 연산장치를 개발하겠다고 발표했는데, 마이크로소프트는 서버용에서 한 발 더 나아가 가정용 PC 시장까지 염두에 둔 ARM 기반 프로세서 개발 전략을 발표하기도 했다.

이러한 변화의 조짐은 x86 의존성이 큰 AMD에서도 나타난 바 있다. AMD)는 가정용 PC는 여전히 x86에 의존하는 반면, 서버 시장의 경우 x864 ARM으로 이원화를 시도하며 ARM 플랫폼 시 장에 진출했다. 2016년 최초의 ARM 아키텍처를 채용한 옵테론A1100 시리즈가 그 시초다. 더욱이 애플이 2020년 출시한 칩 M1 는 비록 고성능 서버가 아닌 PC 시장에 한해 사용되었지만, ARM 기반 제품이 저전력 외에 성능에서도 강점을 보여준 사례다.

2020년 엔비디아가 ARM을 400억 달러(약 47조 4000억 원)에 인수한다고 발표한 배경에는 단순히 서버 시장에서 발휘할 기존 제품과의 시너지 효과에 대한 기대만 있었던 것은 아니다. 향후 세상을 지배할 인공지능과 슈퍼컴퓨팅에서는 저전력이 핵심이라고 판단했기 때문이다. 실제로 엔비디아는 “인텔 x86 아키텍처는 콘 센트에 코드를 꽂는 것만 염두에 뒀을 뿐, 전력의 한계에 대해서 는 고민하지 않았다” 라고 언급한 바 있다.

엔비디아는 이미 자체 프로세서에 ARM을 탑재한 경험도 있 다. 엔비디아의 ARM 인수는 ARM의 현재 점유율이 아니라 미래 점유율을 기대했기 때문임을 엿볼 수 있는 대목이다. 비록 현재 서버 시장에서 ARM의 입지는 제한적이며, ARM의 시세 확장에 는 여전히 비판적인 시각이 존재하는 것도 사실이다. 하지만 서버 시장에 눈독을 들이는 기업들은 점차 ARM을 서버용 설계도로 고려하면서, 서버용 제품의 다양화를 추구하고, 기존 제품과의 시너지를 고민 중이다. 이 과정에서 x86은 성능이라는 본연의 무기로 눈에 띄는 차별화를 구현해야만 현재 시장에서 차지하고 있는 지위를 유지할 수 있을 것이다.

- 흔히 설계라고 하면 자와 컴퍼스, 연필을 이용해 넓은 종이에 무언가 복잡한 그림을 그리는 모습이나 복잡한 선이 가득 얽혀 있는 설계도면이 연상될 것이다. 그러나 반도체 칩 설계는 이러한 과정과 다소 상이하게 이루어진다. 수십억 개의 트랜지스터로 구 성된 칩은 알고리즘을 설계하기도 까다롭지만, 설계도면을 그리기조차 어렵다 기다란 자를 대고 손으로 일일이 60억 개의 배선을 그린다면 고작 선을 긋는 데만 최소 200년이 소요될 것이다!). 이런 이유로 설계도를 그려 나가는 과정에는 EDA (Electronic Design Automation)라 불리는 설계 자동화 툴이 필수적으로 사용된다.

EDA 툴은 설계 자동화라는 이점 외에도 칩 설계 단계에서 칠 의 동작과 성능을 예측할 수 있다는 장점이 있다. 수작업을 통해 설계하던 시절에는 설계가 너무 복잡하고 변수가 너무 많아 칩의 동작을 예측하기가 어려웠다. 실제로 칩이 오동작하는 일도 빈번 하게 발생했다. 이는 칩 개발 과정에서 투자 비용을 낭비하고 개 발 기간이 늘어나는 변수가 됐다. EDA 툴의 등장은 칩 개발에 드 는 비용을 대폭 절감시켰을 뿐만 아니라, EDA 툴 성능 발달이 곧 반도체 업체의 설계 경쟁력으로 이어지는 결과를 낳았다.

- EDA 시장의 미국 독주, 더욱 공고해지는 장벽

EDA는 반도체 칩 설계뿐만 전자회로와 전자기기 설계에도 널리 사용된다. 이들 제품은 다양한 방식으로 설계될 수 있으며, 전자파 차폐 설계 등 특수목적 설계도 빈번히 이루어지므로 EDA 툴은 그 종류가 다양하고, 전 세계적으로 여러 기업에서 개발되고 있다. 그러나 반도체 칩 설계만큼은 시놉시스와 케이던스, 멘토 (독일 지멘스가 인수)의 툴 없이는 이루어지기 어렵다. 이들 기업은 오랜 기간에 걸쳐 반도체 칩의 설계도면 제작부터 작동 검증과 생산까지 도맡아 자동화 가능한 EDA 툴을 독보적으로 개발해왔으며, 다른 설계 자동화 업체를 적극적으로 인수·합병하며 규모를 키워 진입 장벽을 더욱 공고히 해왔다. 오랜 기간 광범위한 설계 노하우를 축적하고 구성 요소를 발전시키면서 이들 기업의 제품 은 대체하기 어려운 수준에 이르렀다. 전 세계적으로 90% 이상의 칩 업체들이 이들 기업의 제품을 기본적으로 사용하고 있는 이유다. 2019년 5월, 미국과 중국의 신경전이 한창인 가운데, 미국의 제재로 반도체 사업을 적극 확대하던 중국의 화웨이와 하이실리 콘이 사업 중단 위기를 맞아 혼란에 빠진 이유도 바로 여기에 있다. 시놉시스, 케이던스, 멘토는 모두 미국에 본사를 두고 있으므 로 반도체 설계는 사실상 미국의 기술 없이는 이루어질 수 없다.

- 문제는 AMD의 부활이었다. CPU 시장에서 쓰라린 패배를 경험한 AMD는 인텔이 신기술 개발에 어려움을 겪는 사이 10m 공 정을 건너뛰고 7 nm 공정 기반의 라이젠(Ryzen) 3세대를 출시했다. 이는 인텔에게도 충격적인 소식이었지만, 인텔의 차세대 CPU를 기다리던 이들에게도 놀라운 발표였다. 인텔과의 경쟁에서 도태되었던 AMD는 어떻게 인텔보다 뛰어난 가성비의 CPU로 시장에 다시 화려하게 등장할 수 있었을까? 이는 AMD가 제조를 모두 파운드리에 의뢰하는 팹리스였기 때문에 가능했다.

AMD는 TSMC의 차세대 공정을 적극적으로 활용했다. 이에 반해 자체 차세대 제조 기술을 개발하는 데 막대한 비용을 투자한 인텔은 차세대 공정을 확보하는 데 어려움을 겪으면서 자체 제조도 그렇다고 해서 못하고 외주를 맡기지도 못하는 신세가 됐다. 하지만 그동안의 설비 투자와 공정 개발에 들인 노력을 물거품이 되도록 내버려둘 수도 없었다. 더욱 충격적인 사실은 AMD가 2019년에 투입한 연구개발비가 15억 달러(약 1조 7000억 원)에 불과하다는 점이다. 같은 기간 인텔은 134억 달러(약 15조 원)를 투입했다. 이들 기업이 CPU 사업만 영위한 것은 아니지만 CPU 개발에 인텔이 AMD 보다 몇 배나 많은 자금을 투자했는데도 선행기술을 확보하지 못한 것이다. 이는 IDM의 한계를 여실히 보여준다.

- TSMC 같은 파운드리는 수많은 팹리스로부터 제조 물량이 끊 임없이 밀려 들어온다. 제품을 만든 후 판매가 만족스러운 수준에 이르지 못하더라도 제조 비용을 모두 팹리스에 전가할 수 있으므 로 손실이 제한적이다. 그러나 IDM은 자체 제품을 제조하는 데 막대한 비용을 쏟아붓기 때문에 제품 판매에 실패할 경우 제조비용을 고스란히 손실로 떠안아야 한다.

- 팹리스는 칩을 설계하지만, 보통은 칩의 알고리즘을 설계하는 작업이 주를 이룬다. 이러한 설계도면은 제조 공정에 대한 사항을 거의 포함하지 않는다. 따라서 칩을 제조하기 전, 제조 공정용 설계도로 다시금 제작하는 과정이 필요하다. 그런데 파운드리에 제조를 의뢰하는 팹리스와 칩의 종류가 매우 다양해서 이들이 가져오는 모든 설계도면을 파운드리가 제조 공정에 맞춰 재설계하 는 것은 불가능하다. 파운드리는 인텔, 퀄컴, 엔비디아 같은 초대형 고객의 물량에 대해 한정적으로 직접 재설계 작업을 수행한다. 그렇다고 해서 팹리스가 모든 제조 공정용 설계를 도맡을 수도 없다. 팹리스는 끊임없이 새로운 칩을 구상하며 변화에 대응해야 하고, 전문성의 한계로 제조 공정을 상세히 알기 어려우므로 제조용 설계도면을 만들 능력도 부재하다. 따라서 파운드리와 팹리스는 이러한 재설계 작업을 디자인하우스라 불리는 기업들에 의뢰한다.

디자인하우스는 새로운 칩을 개발하는 여타 팹리스들과 달리, 다른 팹리스의 설계도면을 제조공정용 설계도로 재설계하는 역 할을 맡는다. 풍부한 디자인 경험과 폭넓은 설계 노하우를 보유한 디자인하우스를 거치면 제조를 의뢰받은 이후 양산에 실패할 가 능성을 최소화할 수 있다. 또한 대규모 디자인을 전문적으로 담당 하므로 재설계 과정에서 필요한 IP 비용을 보다 효율적으로 집행 할 수도 있다. 디자인하우스는 여러 설계도면을 통합하는 작업을 시작으로 설계 검증 작업을 대행하며, 칩 제조에 필요한 마스크제작 작업도 함께 수행한다. 또한, 칩이 완성되면 칩 성능 테스트를 어떤 방식으로 수행할지에 관한 알고리즘도 마련해준다.

- 칩의 재설계를 위해서는 제조 공정에 대한 정보가 일정 부분 파운드리와 공유되어야 한다. 이러한 정보가 모든 팹리스에 노출 된다면 파운드리에 리스크가 될 수도 있다. 그러나 디자인하우스가 디자인 작업을 전문적으로 담당하면 이런 사항을 다른 팹리스 기업들과 공유할 필요가 없다. 이런 이유로 파운드리와 디자인하 우스 사이에는 깊은 신뢰 관계가 필수적이다. 디자인하우스는 자 연스럽게 특정한 파운드리와 깊은 관계를 맺다 보니, 해당 파운드리에 대한 전문적인 역량을 갖추게 된다. 이런 이유로 팹리스는 파운드리에 제조를 맡기는 과정에서 파운드리가 지정하는 특정 디자인하우스를 거치는 것이 일반적이다.

- 반도체 산업 초기에는 디자인하우스가 전혀 필요하지 않았다. 아니, 디자인하우스에 대한 개념 자체가 없었다. 반도체 제조 기 술력이 낮았던 1970~1980년대까지만 해도 팹리스가 제조까지 가능한 수준으로 설계도면을 직접 제작하는 것이 일반적이었다. 그러나 반도체 공정이 발전하고 칩의 종류가 늘어나면서 디자인 을 전문적으로 담당하는 기업들이 생겨났다. 디자인하우스의 역 할은 칩의 재설계에서 벗어나 꾸준히 확대됐는데, 많은 디자인하 우스가 칩의 제조 후 유통 과정까지 책임지고 있다. 팹리스는 설 계에만 특화되어 유통에 문외한인 경우가 많다. 게다가 새로운 유 통망을 하나하나 뚫는 것은 극히 비효율적이다. 이런 이유로 디자인하우스가 이러한 역할을 대행하고 판매 수수료를 취하는 비즈니스 구조가 만들어졌다. 디자인하우스가 칩의 기획부터 유통까지 도맡아 진행하는 서비스를 턴키 서비스라 부른다. 그런데 이러한 사업 모델에는 리스크가 수반된다. 새로운 칩을 개발한 뒤 제품 판매에 실패하면 디자인 하우스로선 수익 창출 기회를 날릴 수밖에 없다.

이처럼 디자인하우스의 역할이 크다 보니 팹리스와 파운드리 는 고민이 많을 수밖에 없다. 팹리스가 칩 제조를 의뢰할 때 파운드리의 제조 역량 외에 디자인하우스의 영업 능력이 얼마나 뛰어난지 함께 고민할 필요가 생긴 것이다. 제품을 엇비슷하게 잘 만들어주는 두 파운드리가 있다면 아무 업체에 제조를 맡겨도 상관 없지만, 각각의 파운드리에 종속된 디자인하우스의 역량에 차이 가 있다면 역량이 우수한 쪽을 선택하는 것이 당연지사다. 이에 따라 디자인하우스의 역량이 곧 파운드리의 영업 성과로 이어지는 구조가 형성됐다. 팹리스를 대상으로 하는 영업도 디자인하우스가 함께 담당한다. 파운드리의 제조 능력을 홍보하는 것 못지않 게 디자인하우스의 역량을 홍보하는 것도 효과적이기 때문이다. 이로 인해 파운드리는 디자인하우스를 더욱 공격적으로 관리하게 됐다. 우수한 디자인하우스를 갖춘 파운드리가 곧 경쟁력이 높은 파운드리라는 공식이 만들어진 것이다.

- TSMC는 세계에서 가장 뛰어난 반도체 제조 기술을 가진 기업 이면서 가장 뛰어난 디자인하우스 역량을 갖춘 기업이다. TSMC 는 대만의 GUC, 알칩 같은 글로벌 디자인하우스 전문 업체 8곳과 긴밀한 관계를 구축해서 VCA(Value Chain Aggregator)를 형성해 왔다. GUC는 연간 매출액 5000억 원, 시가총액 1조 원을 상회하 는 거대한 디자인하우스다. 통신용 비메모리반도체와 가전제품 용 칩 등을 재설계하는 역할을 담당하는데, 세계에서 가장 빠른 칩 출시 역량과 고품질 칩 생산 노하우를 보유한 것으로 유명하 다. TSMC가 2000년대 초반 GUC의 최대 주주로 오른 이유다. 삼성전자는 디자인하우스 역량이 상대적으로 미비하다는 점이 파운드리 사업 확대의 걸림돌로 작용해왔다.

- ASML은 광학 기술의 집합체 또는 유럽 반도체 기술력의 집합체라 불린다. ASML의 성장 동력은 핵심 기술과 부품의 공동 개발, 밸류체인의 완성, 적극적인 인수합병, 유럽의 수많은 일류 연구기관은 물론 TSMC 등 기업과의 밀접한 협력에 기반한다. 다른 곳에 눈독 들이지 않고 차세대 노광기라는 하나의 목표에 수십년간 연구개발 자원을 집중했음은 물론이다. 이러한 요인들이 긍정적인 시너지 효과를 일으키며 반도체 산업을 독점적으로 쥐락펴락하는 현재의 위상을 만들어냈다.

이에 반해, 세계 최고의 광학 기술을 가진 니콘과 캐논은 폐쇄적인 기업 문화로 인해 해외 기업들의 인수합병과 기술 제휴에 소극적인 태도를 보이며 자체 기술 확보에 몰두하다가 ASML의 점유 영역에 진입하는 데 실패하면서 반도체용 광학 시장을 유럽에 완전히 내주고 말았다. 그 결과 ASML이 EUV 시대 최대 수혜주 임은 두말할 필요 없다. EUV가 도입되기 이전부터 ASML의 독주가 이미 시작된 까닭이다.

- EUV 이전에 반도체용 노광기 광원 기술은 사이머와 일본의 기가포톤이 양분해왔다. 두 업체 모두 추가적인 타 업체의 추종 을 불허하는 가운데에서도 사이머는 압도적인 기술력을 바탕으로 기가포톤보다 2배 이상의 높은 점유율을 과시해왔다. 그러다 독보적인 LPP 기술력을 요구하는 EUV에서는 사실상 사이머의 독점이 지속됐다. 도널드 트럼프 대통령이 재임한 동안 펼쳐진 미·중 무역전쟁에서 ASML이 EUV 장비를 중국에 판매하는 것 을 포기한 이유도 광원 기술에 있다. EUV 광원 원천 기술은 사이 머를 중심으로 미국이 보유하고 있었다.

ASML은 2012년 사이머를 무려 37억 달러(약 4조 2000억 원)에 인수했다. 거금을 주고 인수함에 따라 사이머의 광원 기술이 곧 ASML의 기술이 됐는데도 ASML이 노광기를 자유롭게 수출할 수 없었던 이유는 광원 기술이 각국에서 전략 물자로 관리되는 첨단 기술이기 때문이다. 전략 물자로 관리되는 기술은 바세나르 협약에 따라 수출될 수 없다. 실제로 미국은 이 협약을 이유로 네덜란드에 EUV 수출 금지를 직접 요청하기도 했다. EUV 기술이 전쟁 무기로 전용될 수 있다는 표면적인 이유도 있지만, 중국이 반도체 기술을 확보할 것을 우려하는 속내가 더욱 크게 작용했을 것이다. 물론 이런 이유 외에도 ASML로선 굳이 중국에 장비 를 수출할 필요가 없었다. 향후 수년 이상 장비를 사갈 업체들이 줄을 서 있고 생산 물량 확대를 거듭해도 공급이 수요의 절반도 따라가지 못하는 형국에 중국이 있으나 없으나 어차피 가만히 앉아서 이루어지는 돈벌이는 변함없이 지속될 것이었기 때문이다.

- 식각 장비는 수많은 물질을 깎아내는 특성상 장비 내부가 빠르 게 오염되며 장비를 구성하는 핵심 부품, 웨이퍼를 지지하는 지지 부품 등이 쉽게 부식된다. 이런 이유로 식각 장비는 반드시 일정한 주기마다 진공을 모두 해제하고 내부 세척 작업과 부품 교체작업을 수행해야 한다. 작업이 진행되는 동안에는 당연히 식각 장비를 가동할 수 없으므로 반도체 제조 생산성이 크게 떨어지며 인력 투입으로 인한 비용이 발생한다. 비용 절감을 위해 유지보수를 최소화하는 방법을 고안하는 것은 결국 장비업체들의 몫이다.

램 리서치, 어플라이드 머티리얼즈, 도쿄 일렉트론은 장비 자동화를 통해 유지보수 횟수와 시간을 최대한 단축하려고 시도하고 있지만 자동화 기술을 확보하는 것은 결코 쉬운 일이 아니다. 이 런 자동화 기술은 인공지능 기술과 묶여 장비 관리 종합 플랫폼으 로 발전하고 있다. 장비 내부 환경을 실시간으로 감시하며, 잦은 교체가 필요한 장비 부품을 자동으로 교체해주는 시스템을 결합 해 종합적인 장비 시스템 제어 플랫폼을 구축하려는 것이다. 이를 통해 생산성이 향상되어 반도체 업체들은 더 적은 수의 장비를 운 영하면서도 웨이퍼 출하량을 늘릴 수 있고, 장비업체들은 장비 가 격을 높여 수익성을 확보할 수 있다.

- 트렌치와 스택 공정을 이용해 만든 구조물은 모두 겉에서 보기엔 땅을 수직으로 뚫어 만든 우물과 유사하게 생겼지만, 두 공정에는 엄연한 차이가 있다. 트렌치 공정은 위에서부터 아래로 웨이퍼상의 물질을 뚫고 들어가며 수직 구조물을 만드는 공정인 반면, 스택 공정은 아래에서부터 위로 새로운 물질을 쌓으며 수직 구조물을 만드는 공정이다. 트렌치는 땅을 뚫으며 지하가 깊은 건축물을 짓는 것과 같고, 스택은 땅 위로 고층 빌딩을 짓는 것과 같다.

- 트렌치 공정은 깊숙한 구조물을 미세하게 뚫어야 하고, 다시 길게 형성된 세부 구조물에 미세하게 소재를 쌓아 채우는 방식에 기반하므로 오직 쌓는 것에만 집중하는 스택보다 공정이 복잡하고 비용이 많이 소모될 수밖에 없다. 미세한 영역에서의 공정이 많아 지므로 수율 확보도 더욱 어려워진다. 반면 스택 공정은 땅 위에 건축물을 쌓아 올라가는 것과 같으므로 완성된 구조물이 밖에서 훤히 들여다보이는 이점이 있다. 지하 깊숙이 구조물을 만들면 외 부에서 구조물을 관찰할 수 없으므로 건축물을 살펴보기 위해서 는 또 한번 땅을 파야 하듯, 트렌치 공정은 문제가 발생할 경우 칩 분석 시간 지연이 필연적으로 발생한다.

물론 스택 공정에도 단점은 있다. 쌓아 올린 구조물의 품질이 트렌치 방식보다 떨어지므로 D램의 성능 저하와 불량 발생 우려가 존재하고, 트렌치 방식보다 거대한 구조물을 쌓아 형성하므로 구조물 미세화를 위한 노력이 필요하다. 거대한 구조물을 웨이퍼 에 가득 쌓아 올린 만큼 구조물 상단부의 표면이 평평하지 못한 문제도 있다. 이런 이유로 이 위에 신호 전달을 위한 수많은 배선 회로를 만드는 과정에서 여타 칩과 공정 호환이 이루어지지 않는 다. 그럼에도 불구하고 스택 방식은 트렌치 방식보다 공정이 단순하고 비용 절감에 유리해서 결국 D램 제조 공정의 표준으로 자리잡았다

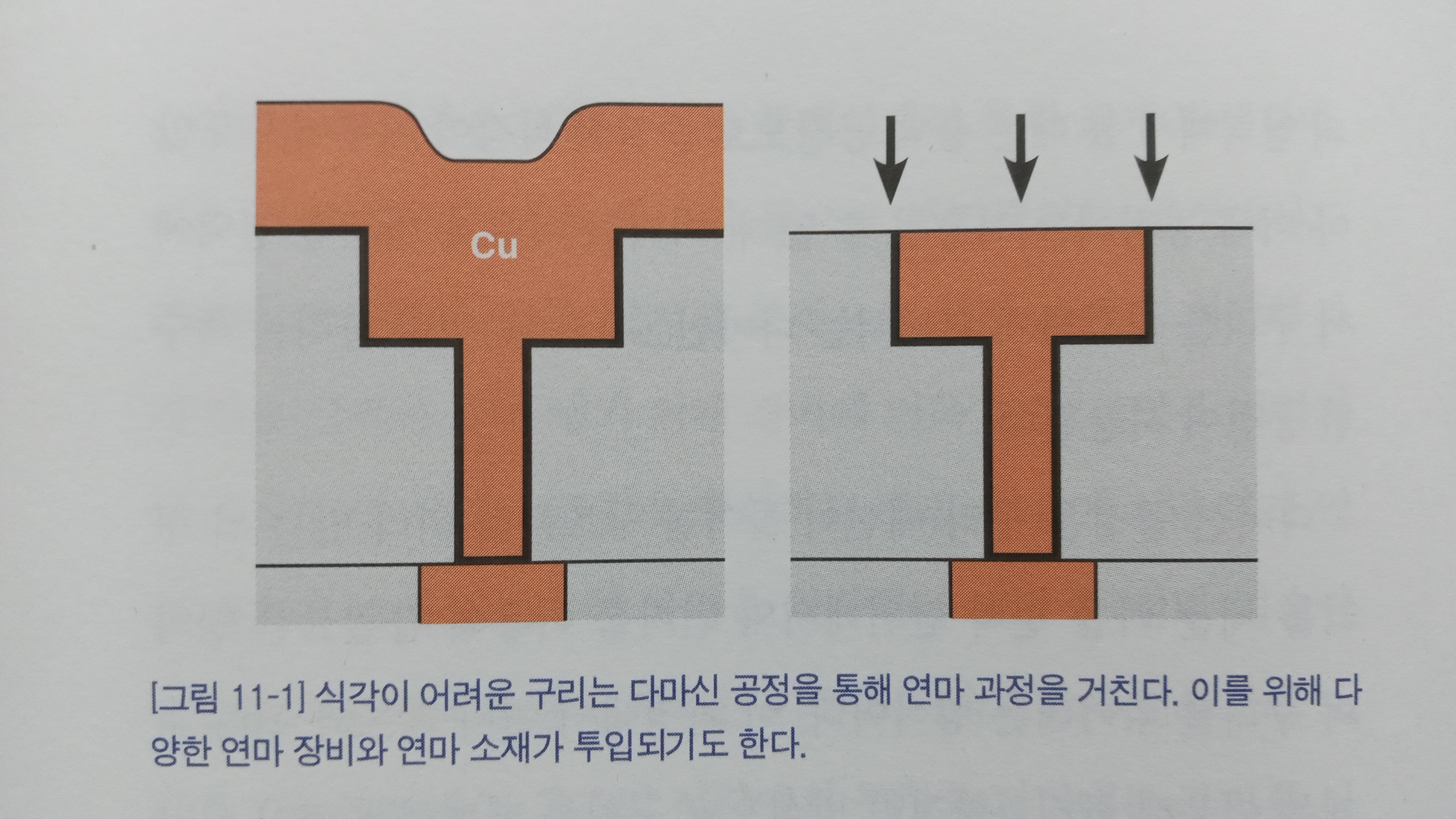

- 금속의 전도성은 전자가 금속 원자 사이를 얼마나 잘, 그리고 얼마나 빠르게 이동할 수 있는가에 의해 결정된다. 전자가 수월하게 이동하기 위해서는 다른 입자와 충돌하지 않고 최대한 먼 거리를 이동해야 한다. 이러한 거리를 평균자유경로(mean free path)라고 한다. 상온에서 구리 내 전자의 평균자유경로는 40m 정도로 알려져 있다. 구리의 선폭이 40m보다 작아지면 전자가 더욱 먼 거리를 가지 못하고 벽면과의 충돌과 산란이 활발히 발생한다. 이로 인해 구리의 비저항이 높아지는 저항 크기 효과 (resistivity size effect)가 발생한다. 또한 미세화될수록 지속적으로 전기 신호가 흐르며 구리 이온들이 밀리는 일렉트로마이그레이션 (electromigration) 현상이 더욱 두드러진다. 구리 원자들의 배열이 흐트러지면서 배선이 단절되는 결과로 이어지는 것이다. 이러한 이유로 40m 이하의 미세한 영역에서 구리는 제 성능을 발휘하지 못한다. 실제로 10m 두께의 구리는 크기가 작다는 이 유만으로 일상의 구리에 비해 비저항이 10배 이상 높아진다(똑같은 물질인데도 말이다!) . 배선의 저항이 증가하면 소비 전력과 발열이 크게 높아지고, RC 지연에 의해 신호의 전달 속도가 느려져(이에 대해서는 다음 파트에서 살펴보겠다!) 칩의 빠른 동작이 어려워진다. 이는 반도체 미세화를 어렵게 만드는 또 하나의 요인이다.

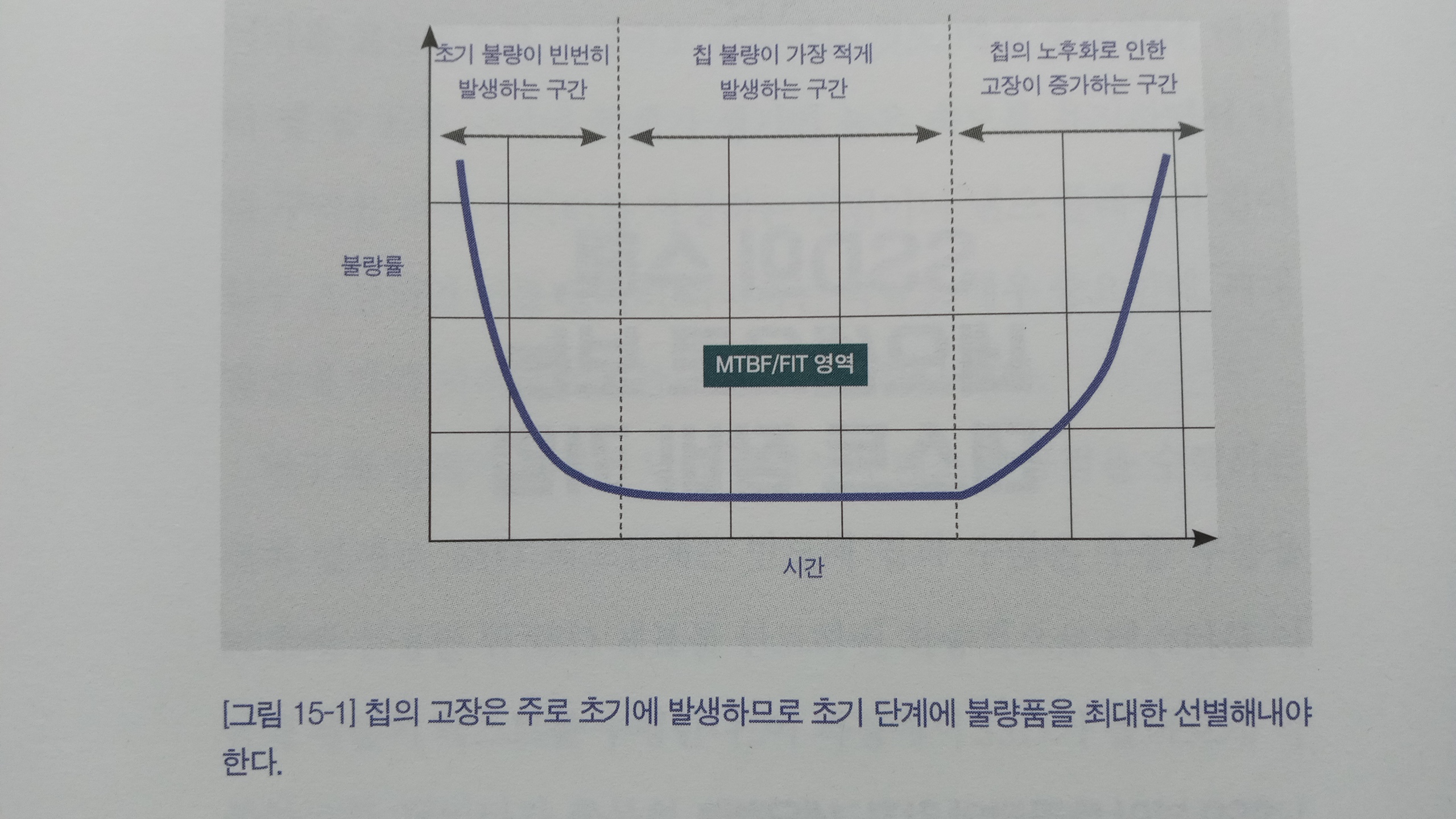

- 웨이퍼 레벨 테스트에서는 프로브 팁 (probe tip)이라 불리는 여 러 개의 뾰족한 금속 팁들이 웨이퍼에 접촉해 전기적 신호를 주고 받으며 칩의 성능을 검사한다. 프로브 스테이션(Probe Station)이라 불리는 장비가 이 역할을 담당한다. 프로브 스테이션이란 이름 자 체가 프로브 팁이 잔뜩 모여 있는 공간이란 의미를 갖는다. 프로 브 스테이션은 프로브 핀을 고정하기 위한 일련의 부품들로 구성 되어 있는데, 칩이 만들어지는 과정에서 가장 미세한 영역을 측정 하는 장비이므로 여러 종류의 반도체 검사 공정 중 가장 높은 기 술력이 필요하다. 이에 따라 프로브 스테이션 장비는 주로 기술력이 높은 외국 검사 장비 업체들이 독주하는 영역이었다.

다만 반도체 칩의 종류에 따라 검사의 난이도가 상이한데, 낸드 플래시는 D램 또는 고사양 비메모리 칩 대비 프로브 팁의 수가 상대적으로 적기 때문에 검사 공정의 난이도도 비교적 낮은 편이다. 이에 따라 샘씨엔에스와 같은 국내 기업들도 낸드 플래시용 검사 장비와 부품을 중심으로 시장에 진입하여 영역을 꾸준히 확대해왔다.

웨이퍼 레벨 테스트는 전기 신호를 주어서 칩을 분류한다는 의미에서 EDS (Electrical Die Sorting) 테스트라고 불린다. 프로브 스테이션에 설치된 프로브는 웨이퍼를 이동시켜가며 웨이퍼의 넓은 영역을 검사한다. 프로브 스테이션은 전기적 신호를 흘려 양품과 불량품을 구분해주며, 불량품이 생산된 것으로 확인될 시 후공정에 들어가기 전 해당 칩을 버리는 조치가 취해진다.

- 문제는 반도체 미세화에 따라 웨이퍼에 만들어지는 칩의 수가 꾸준히 증가하고 있다는 점이다. 따라서 웨이퍼 레벨 테스트로 모든 칩의 성능을 평가하려면 수백수천 번 테스트를 반복할 수 밖에 없다. 이는 반도체 생산성을 심각하게 떨어뜨리는 결과를 초래한다. 심지어 아직 칩이 완성된 단계도 아니다. 중간 제조 과 정에서의 테스트는 간단할수록 유리하다. 이에 따라 웨이퍼 레 벨 테스트를 보다 수월히 수행하기 위해 연구개발자들은 잔머리를 굴렸다.

그 결과, 웨이퍼에 처음 칩을 만들 때부터 오직 웨이퍼 레벨 테스트에만 사용할 회로를 함께 만드는 방법이 고안됐다. 전공정을 수행하는 과정에서 칩의 동작을 위한 각종 회로 외에 여러 칩의 성능을 한번에 테스트하기 위한 테스트 전용 회로를 칩들 사이에 만들어두는 것이다. 프로브 팁이 몇 개의 회로에 닿아 전기 신호를 인가하면 한번에 여러 칩의 성능이 동시에 확인된다. 불량 칩이 섞여 있으면 비정상적인 측정 결과가 출력되고, 회로 설 계 알고리즘에 따라 여러 칩 중 어떤 칩이 불량품인지 찾아낸다. 검사 수를 최대한 줄이기 위해 여러 칩을 한번에 측정할 수 있도록 엔지니어들은 잠시 사용하고 버려질 회로까지도 잘 설계해야하는 것이다.

- 이처럼 전공정을 통한 칩 성능 향상이 점차 한계를 나타내자 반도체 업체들은 칩의 이종화를 통한 칩의 성능 향상으로 눈을 돌리기 시작했다. 칩의 퍼포먼스를 전반적으로 향상시키기 위해서는 칩 자체의 성능이 개선되어야 한다는 기존 인식과 달리, 완성된 칩들을 잘 이어 붙여주기만 해도 전자기기의 성능을 추가로 개선할 수 있다. 무어의 법칙(Moore's Law, 반도체 집적회로의 성능이 18개월마다 2배로 증가한다는 법칙)과는 전혀 다른 방식으로 기술적 진보가 이루어진 것이다.

- 이에 따라 패키징 공정은 단일 칩의 패키징 기술 발전과 함께 POP Package On Package), SiP (System in Package), TSV(Through Silicon V2) 등 서로 다른 칩들의 적층 패키징, 이종 칩의 단일화 패키징 같은 새로운 방향으로 발전했고, 이들이 모여 차세대 어드밴스드 패키징 (Advanced Packaging)으로 발전하고 있다. 앞서 설명한 제주반도체가 영위하는 MCP 사업도 이러한 패키징 기술의 변화에 근거한다.

D램과 낸드 플래시가 전자기기 내에 별개로 실장될 때보다 수직으로 적층된 상태로 실장되면, 두 칩 사이에 데이터가 더욱 빠르게 오갈 수 있으며 전력 손실이 줄어든다. MCP는 패키징 공정에 들어선 두 칩을 대상으로 칩의 적층 패키징 공정이 추가된다는 것이 특징이다. 적층된 칩의 두께를 최소화하기 위해 웨이퍼를 얇게 깎아내는 공정도 거친다. 수십 마이크로미터 단위의 얇은 집을 적층하며, 주로 공간이 제한된 모바일 기기에 탑재한다. 적층되는 칩의 수에 따라 DDP (Double Die Packaging), TDP (Triple Die Jackaging), ODP (Quad Die Packaging) 등으로 나뉜다. 적층 수가 늘어날수록 웨이퍼를 더욱 얇게 깎아야 하는데, 이 과정에서 나타나는 칩의 휨 현상을 최소화하기 위해 레이저 다이싱 (Laser dicing)이나 마운트 테이프(mount trape) 등 추가 공정과 소재들이 동원된다.

이로 인해 기존 레이저 기업들의 위상이 높아졌을 뿐만 아니라, 기존에는 톱만 사용하던 업체도 점차 레이저에 관심을 갖게 된 것이다. 이종 칩 패키징은 이처럼 추가적인 후공정이 필요하지만, 전공정을 통해 동일한 성능 향상 효과를 내기 위해서는 포토, 증착, 식각 공정 모두가 총동원되어야 한다는 점을 고려하면 상당히 효율 적인 대안이다.

패키징 기술의 변화는 비메모리반도체와 메모리반도체를 가 리지 않고 활발히 이루어지며, 비메모리반도체와 메모리반도체의 이종 패키징도 적극적으로 적용된다. 메모리 칩을 수직 적층하면 고속 데이터 전송이 가능해질 뿐만 아니라, 동일한 면적 내 에서 메모리 용량을 극대화한 제품을 출시할 수 있으며, 메모리 반도체와 비메모리반도체를 수직 적층해서 이종 패키징할 경우 비메모리반도체가 실시간으로 처리하는 다량의 데이터를 고속으로 메모리 반도체에 저장해 월등히 많은 데이터를 처리할 수있게 된다.

대표적인 사례가 스마트폰에 활발히 도입되는 고속 촬영 기능 이다. 과거의 핸드폰은 카메라에 입력된 화상 이미지 신호들이 전자제품 내 별도 영역에 설치된 메모리반도체까지 도달하는 데 오래 걸려 촬영 후 일정 시간 동안 카메라 작동이 멈출 수밖에 없었다. 그러나 현재는 서로 다른 칩이 수천 개의 수직 비아(via) 배선 으로 연결되어 있어서 고성능 센서가 시도 때도 없이 만들어내는 이미지 데이터를 병목현상 없이 메모리에 즉시 전송할 수 있으며, 초당 수십 장의 사진을 찍어내며 빠르게 이동하는 피사체도 왜곡없이 담아내 고품질 사진을 만들어낼 수 있게 됐다.